base address register|pcie bar address mapping : Pilipinas Learn about the base address register in ARM instruction set and exception handlers. See examples of different addressing modes, index methods, and exception codes. Best Hobby Shops in Kota Damansara, Petaling Jaya, Selangor, Malaysia - Hobby Forge, Anime Trend, FUNDERLAND, Cards & Hobbies, Feo, XL Shop, Classroom Cafe, Big Bang Toyz, Wira Games & Hobbies, The Corner Shop . The Best 10 Hobby Shops near Kota Damansara, Petaling Jaya, Selangor, Malaysia. . From toy cars to nano blocks or .

PH0 · virtual address space

PH1 · usps new address registration

PH2 · resizable base address register

PH3 · pcie resizable base address register

PH4 · pcie bar address mapping

PH5 · new construction address registration

PH6 · memory address register

PH7 · lspci gpio base address

PH8 · Iba pa

Jackpot Capital Casino Promotions and Bonuses. Jackpot Capital new players can enjoy a 10 Free no deposit code and then go on to enjoy an especially generous Welcome Bonus as depositing players. As soon as you make an initial deposit to play for real money prizes you’ll be gifted with a 100% match bonus up to $100 and bonus code 100 free .

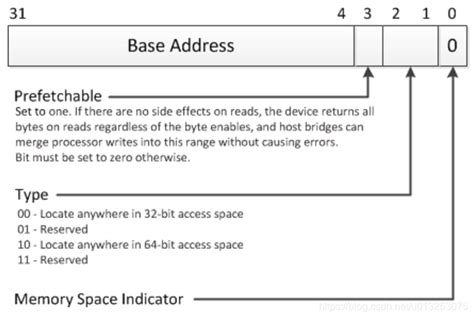

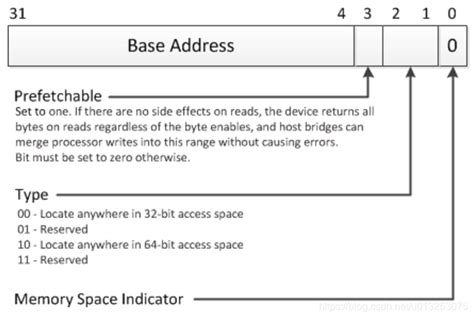

base address register*******Learn about the base address register in ARM instruction set and exception handlers. See examples of different addressing modes, index methods, and exception codes.To address a PCI device, it must be enabled by being mapped into the system's I/O port address space or memory-mapped address space. The system's firmware (e.g. BIOS) or the operating system program the Base Address Registers (commonly called BARs) to inform the device of its resources configuration by writing configuration commands to the PCI controller. Because all PCI devices are in an inactive state upon system reset, they will have no addresses assigned to the.Base Address Register (BAR) Settings. V-Series Avalon-MM DMA Interface for PCIe Solutions User Guide. Download PDF. View More. Document Table of Contents. 1. . Each BAR holds the address of a communication area. This address can be set and read by the operating system as part of the larger device configuration. For each .Quick Fix: The Base Address Register (BAR) in PCIe provides a way to map memory and I/O addresses to the device. It is used to establish communication between the host and .

Base Address Register (BAR) Settings. 3.3. Base Address Register (BAR) Settings. The type and size of BARs available depend on port type. Table 19. BAR Registers. If you .base address register pcie bar address mapping push rbp mov rbp, rsp mov rax, qword ptr fs:[0]; grab the base address of the thread-local storage area lea rax, [rax + x@TPOFF]; calculate the effective address . BX: This is called a Base register. It has 16 bits and is split into two registers with 8 bits each, BH and BL. An address register is the BX register. It typically includes a data pointer for indirect addressing .

Base address. In computing, a base address is an address serving as a reference point ("base") for other addresses. Related addresses can be accessed using an .base address register ベースレジスタ ベースレジスタ(英:base register)とは、レジスタの一種でプログラムをメモリ上にロードした時の先頭のアドレスを記憶しておくためのものです。 レジスタとは レジスタ(英:re . レジスタ(英:register)とは、CPU内部にある記 .

pcie bar address mapping Base Address Register: PCI configuration space는 장치를 찾을 때만 이용하는 공간으로 매우 용량이 작습니다. 일반적으로 Device driver는 이 공간보다 용량이 더 크기 때문에 메모리에 적재합니다. . Base. Addressing via the base register adds one layer of indirection over absolute addressing: instead of an absolute address encoded into the instruction’s displacement field, an address is loaded from the specified general-purpose register (any GPR! Hooray!). IMPORTANT TERMS. Starting address of memory segment.; Effective address or Offset: An offset is determined by adding any combination of three address elements: displacement, base and index.. Displacement: It is an 8 bit or 16 bit immediate value given in the instruction. Base: Contents of base register, BX or BP.; Index: .

From your article : Base address Registers (or BARs) can be used to hold memory addresses used by the device, or offsets for port addresses. Typically, memory address BARs need to be located in physical ram while I/O space BARs can reside at any memory address (even beyond physical memory). The Type field of the Memory Space BAR . PCISIG 문서를 읽어보면.. •Base Address Register, BAR. Base Address Registers exist within Configuration Space and are used to determine the amount of system memory space needed by a Function and to provide the base address for a mapping to Function memory space. A Base Address Register may map to memory .4.2. 基地址寄存器(Base Address Register). 4.2. 基地址寄存器(Base Address Register). 表 16. BAR寄存器. 如果选择64-bit可预取存储器 (64-bit prefetchable memory),则2个连续的BAR会被组合成一个64-bit可预取BAR;您必须将较高编号的BAR设置为 Disabled 。. 不支持非可预取64‑bit BAR . #Linux #FOSS #FLOSS #PCIHere I am with a new series of videos. This time about GNU/Linux and PCI (Express). I want to show you, how to access PCI (Express) d. 其它的我们暂时不看,我们看看重要的BAR(Base Address Register)。 对Endpoint Configuration(Type 0),提供了最多6个BAR,而对Switch(Type 1)来说,只有2个。 . Bus Number + Device + Function就唯一决定了目标设备; Ext Reg Number + Register Number相当于配置空间的偏移。 BX: This is called a Base register. It has 16 bits and is split into two registers with 8 bits each, BH and BL. An address register is the BX register. It typically includes a data pointer for indirect addressing that is based, based indexed, or register-based. CX: This is known as the Count register. Its 16 bits are split into two 8-bit . Usually, the Base Address Register is the record of the device address beginning at the memory. This register is usually used for two specific purposes, such as: To specify the amount of memory required by a device to map it into the main memory; To hold the base address after enumeration of the devices where the block of mapped .

In computing, a base address is an address serving as a reference point ("base") for other addresses. Related addresses can be accessed using an addressing scheme.. Under the relative addressing scheme, to obtain an absolute address, the relevant base address is taken and an offset (aka displacement) is added to it. Under this type of scheme, the .BAR (Base Address Register) is a memory address assigned to a PCIe device. Each PCIe device has at least one set of PCI configuration space registers. PCI configuration space is used to direct the device’s behavior, including the location of its memory-mapped I/O. Every PCIe device has a set of function registers that contain the information .Intel® Arria® 10 or Intel® Cyclone® 10 GX Parameter Settings x. 3.1. Parameters 3.2. Intel® Arria® 10 or Intel® Cyclone® 10 GX Avalon-ST Settings 3.3. Base Address Register (BAR) and Expansion ROM Settings 3.4. Base and Limit Registers for Root Ports 3.5. Device Identification Registers 3.6. PCI Express and PCI Capabilities Parameters 3.7.

Base Address Register (BAR) Settings. 3.4. Base Address Register (BAR) Settings. Each function can implement up to six BARs. You can configure up to six 32-bit BARs or three 64-bit BARs for both PFs and VFs. The BAR settings are the same for all VFs associated with a PF. Table 11. BAR Registers. Parameter. Resizable BAR的全称是“Resizable Base Address Register”,即可调整大小的基址寄存器,简单点说就是“解锁显存访问限制”,是由NVIDIA英伟达研发的一项标准化的PCI Express接口技术,于2021年开始在显卡上搭载.PCI 中的base address register. PCI設備有很好的可配置型和易操作性,這很大方面要歸功於其地址空間的可動態分配的特性。. 而動態分配地址空間就是依賴於BAR(base address register)實現的。. BAR是PCI配置空間中從0x10 到 0x24的6個register,用來定義PCI需要的配置空間大小 .

PCI 中的base address register. PCI设备有很好的可配置型和易操作性,这很大方面要归功于其地址空间的可动态分配的特性。. 而动态分配地址空间就是依赖于BAR(base address register)实现的。. BAR是PCI配置空间中从0x10 到 0x24的6个register,用来定义PCI需要的配置空间大小 .

Pokémon Girl Hunter is a great Pokemon Fire Red Hack made by fz15 who is the author of other good Hacks. Its actually a really good lengthy and even original story taking place in the pokemon world where team rocket has .

base address register|pcie bar address mapping